# Automotive case study

Using Open Source to take 11 chips down to 1 In 3 months!

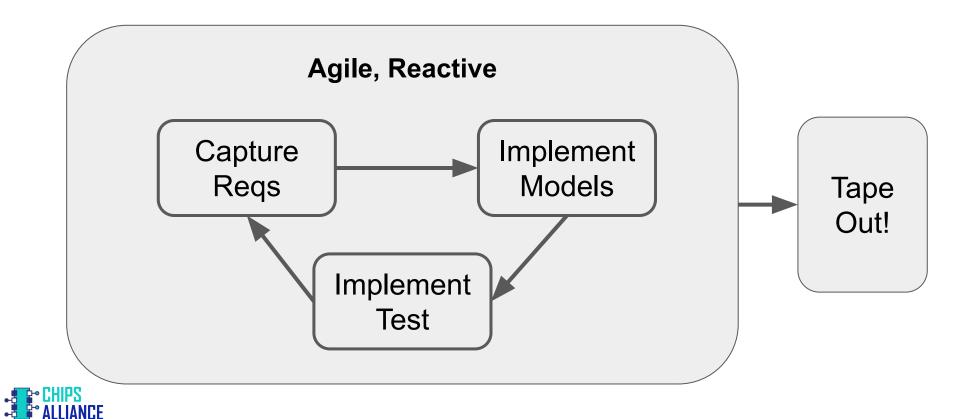

# From no requirements to tapeout in 3 months?

# Reduce Software Load?

### Let's See!

# From no requirements to tapeout in 3 months?

# Reduce Software Load?

### Let's See!

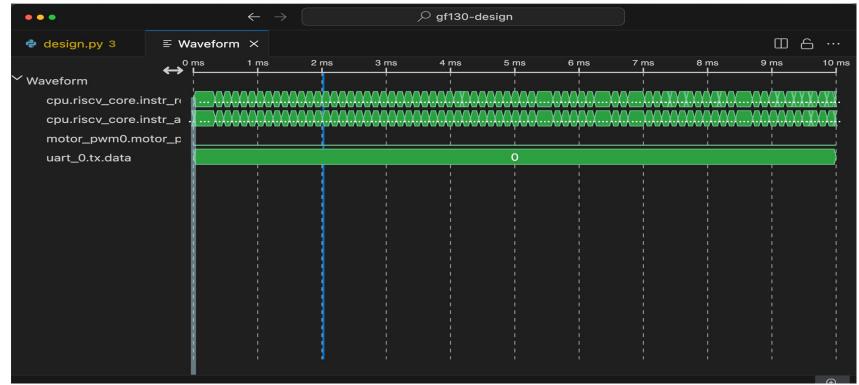

| RTL DEBUGGER                                                                                                                                                                 |        | 🕏 serial.py                                     | 🕏 pwm.py 9+ 🔸                                                                                               | $ ho$ $\sim$ $\square$ $\cdots$                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| → HIERARCHY                                                                                                                                                                  |        | 29 class                                        | s > ∉ pwm.py > 全 PWMPerip<br>PWMPeripheral(wiring.Compo<br>f elaborate(self, platform                       | onent):                                               |

| Current Scope: uart_0.tx<br>> {} user_spi_1 module<br>> {} user_spi_2 module<br>{} wb_arbiter module<br>VARIABLES                                                            |        | 79       80       81       82       83       84 | <pre>#synchronizer stop = Signal() motor_pv m.submodules += FFSynchi m.d.comb += selfstop_i</pre>           | vm0.U\$1.stop=0 motor_pwr<br>ronizer(i=self.pins.stor |

| <ul> <li>&gt; [@] bitno [3:0] = 0</li> <li>(@] clk = 1</li> <li>&gt; [@] data [7:0] = 427819008</li> <li>&gt; [@] divisor [23:0] = 217</li> <li>[@] fsm_state = 0</li> </ul> | 30     | 85 ~<br>86<br>87 ~<br>88<br>89<br>90 ~<br>91    | <pre>with m.If((selfconf.f.</pre>                                                                           | q(count+1)<br>q(0)<br>.val.data > 0) & (count         |

| WATCH > [@] instr_rdata_i [31:0] = 4 > [@] instr_addr_o [31:0] = 1 [@] motor_pwm0_pwm_o > [@] data [7:0] = 0                                                                 | 050896 | 92 ~<br>93<br>94<br>95 ~<br>96<br>97            | <pre>with m.Else():<br/>m.d.comb += self.pir<br/>with m.If(count &gt;= self.<br/>m.d.sync += count.ec</pre> | ns.pwm_o.eq(0)<br>denom.f.val.data):                  |

| < Chi                  | ipFlow public demos | ChipFlow                                                               |         |                      |  |  |  |  |

|------------------------|---------------------|------------------------------------------------------------------------|---------|----------------------|--|--|--|--|

| gf130-design           |                     | < <u>gf130-design</u>                                                  |         |                      |  |  |  |  |

| ۲                      | Builds              | Build 189                                                              |         |                      |  |  |  |  |

| đ                      | Manufacturing       | Name c258572804f5d221744debf376ef60c21f4ff050-<br>dirty.20240914591455 | Input f | Input files          |  |  |  |  |

| \$                     | Project settings    | Created 14/09/2024, 16:59:57                                           |         | config.json          |  |  |  |  |

|                        |                     | Status 🗸 success                                                       |         | rtlil.il             |  |  |  |  |

|                        | Report              |                                                                        | Result  | files                |  |  |  |  |

|                        |                     | (i) Info                                                               | Roodie  |                      |  |  |  |  |

|                        |                     | Unknown max frequency, no clock provided                               |         | customer-report.json |  |  |  |  |

|                        |                     | Gates 130251                                                           | Ĥ       | cli-output.txt       |  |  |  |  |

| Area used 5.5% of 20 m |                     | Area used 5.5% of 20 mm2                                               | A       | gds.gds              |  |  |  |  |

|                        |                     | REQUEST MANUFACTURE                                                    |         |                      |  |  |  |  |

| Runner details         |                     |                                                                        |         | results.json         |  |  |  |  |

|                        |                     | Started 14/09/2024, 17:02:13                                           |         |                      |  |  |  |  |

|                        |                     | Finished 14/09/2024, 17:29:44                                          |         |                      |  |  |  |  |

|                        |                     | Build time 29.8 mins                                                   |         |                      |  |  |  |  |

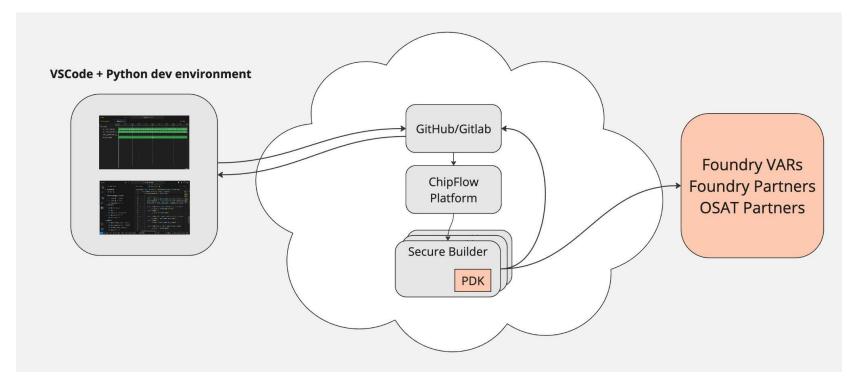

#### A different approach to design house

#### A different approach to design house

# **Biggest challenges?**

# **Biggest challenges?**

## GF130 BCD

# **Biggest challenges?**

## **Functional Safety**

## Outcomes

# CASE STUDY

# 11 to 1 in 3 months

A leading luxury automotive OEM needed a path forward for overhauling their **electronic architecture.**

The **ChipFlow platform** was used to deliver an all-in-one custom ASIC against their requirements for **full door functionality** connected by **Ethernet TIS.**

Initial test chip was designed in **3 months**, at a cost of **\$300k**, giving the customer a path to full control of their platform needs. This custom solution replaced **4 control units** and **11 ICs** with **1 IC**, representing a saving of **80%** on the budget for harness and electronics.

## **Questions?**

### Rob Taylor <rob.taylor@chipflow.io